QUOTE(Amal @ Nov 4 2010, 07:09 PM)

Already emailed to their support... no response...

Yeah, they do that.

Are you using the

Technical Inquiry page at Asus member/support page? They will respond to you, don't worry about it (maybe after a week

). Remember to follow up with Asus support/Royal Club since your A42JA should support DDR3 1333 since it have i7 processor which utilize it (chipset PM55 & HM55 already support DDR3 1333).

Added on November 4, 2010, 7:59 pmQUOTE(RedDevils88 @ Nov 4 2010, 07:12 PM)

mine is not visible.. but what does it do?

(Source)The System Management Bus (abbreviated to SMBus or SMB) is a single-ended simple two-wire bus for the purpose of lightweight communication. Most commonly it is found in computer motherboards for communication with the power source for ON/OFF instructions.

It is derived from I²C for communication with low-bandwidth devices on a motherboard, especially power related chips such as a laptop's rechargeable battery subsystem (see Smart Battery Data). Other devices might include temperature, fan or voltage sensors, lid switches and clock chips. PCI add-in cards may connect to a SMBus segment.

I believe the "missing/hidden" SMBUS controller is the reason why SPD information is not visible with CPU-Z v1.55 because it can't communicate with SMBUS controller. It only displayed after we launch HWiNFO32 Program. Newer version, CPU-Z v1.56, able to scan & communicate with the "missing/hidden" SMBUS controller without any third party program. The same way HWiNFO32 Program & Everest (beta version) can scan/detect the "missing/hidden" SMBUS controller.

The SMBUS controller only appear on Device Manager after I inject it in ACPI table (DSDT). I currently dual-boot with Mac OS X (purely for experiment & research). When using Mac OS X you need to use modified DSDT just like linux on unsupported computer. This is what I inject in the DSDT:-

CODE

Device (SBUS) // Intel SMBus Controller

{

Name (_ADR, 0x001F0003)

OperationRegion (SMBP, PCI_Config, 0x40, 0xC0)

Field (SMBP, DWordAcc, NoLock, Preserve)

{

, 2,

I2CE, 1

}

OperationRegion (SMPB, PCI_Config, 0x20, 0x04)

Field (SMPB, DWordAcc, NoLock, Preserve)

{

, 5,

SBAR, 11

}

OperationRegion (SMBE, PCI_Config, 0x04, 0x02)

Field (SMBE, AnyAcc, NoLock, Preserve)

{

IOSE, 1 // I/O Space Enable

}

OperationRegion (SMBI, SystemIO, ShiftLeft (SBAR, 0x05), 0x10)

Field (SMBI, ByteAcc, NoLock, Preserve)

{

HSTS, 8, // Host Status

Offset (0x02),

HCON, 8, // Host Control

HCOM, 8, // Host Command

TXSA, 8, // Transmit Slave Address

DAT0, 8, // Host Data Byte 0

DAT1, 8, // Host Data Byte 1

HBDR, 8, // Host Block Data

PECR, 8, // Packet Error Check

RXSA, 8, // Receive Slave Address

SDAT, 16 // Receive Slave Data

}

Name (SBOK, Zero)

Method (ENAB, 0, NotSerialized) // Enable Method

{

Store (One, IOSE)

Store (One, SBOK)

}

Method (DISB, 0, NotSerialized) // Disable Method

{

Store (Zero, SBOK)

}

Method (SSXB, 2, Serialized) // SMBus Send Byte(Arg0:Address, Arg1:Data)

{

If (STRT ()) // Is the SMBus Controller Ready?

{

Return (Zero) // Failure

}

// Send Byte

Store (Zero, I2CE) // SMBus Enable

Store (0xBF, HSTS)

Store (Arg0, TXSA) // Write Address

Store (Arg1, HCOM) // Write Data

Store (0x48, HCON) // Start + Byte Data Protocol

If (COMP ()) // Check if last operation completed

{

Or (HSTS, 0xFF, HSTS) // Clean up

Return (One) // Success

}

Return (Zero) // Failure

}

Method (SRXB, 1, Serialized) // SMBus Receive Byte(Arg0:Address, Return:0xffff=Failure, Data (8bit)=Success)

{

If (STRT ()) // Is the SMBus Controller Ready?

{

Return (0xFFFF)

}

// Receive Byte

Store (Zero, I2CE) // SMBus Enable

Store (0xBF, HSTS)

Store (Or (Arg0, One), TXSA) // Write Address

Store (0x44, HCON) // Start

If (COMP ()) // Check if last operation completed

{

Or (HSTS, 0xFF, HSTS) // Clean up

Return (DAT0) // Success

}

Return (0xFFFF)

}

Method (SWRB, 3, Serialized) // SMBus Write Byte

{

If (STRT ()) // Is the SMBus Controller Ready?

{

Return (Zero) // Failure

}

Store (Zero, I2CE) // SMBus Enable

Store (0xBF, HSTS)

Store (Arg0, TXSA) // Write Address

Store (Arg1, HCOM) // Write Command

Store (Arg2, DAT0) // Write Data

Store (0x48, HCON) // Start + Byte Protocol

If (COMP ()) // Check if last operation completed

{

Or (HSTS, 0xFF, HSTS) // Clean up

Return (One) // Success

}

Return (Zero) // Failure

}

Method (SRDB, 2, Serialized) // SMBus Read Byte(Arg0:Address,Arg1:Command, Return:0xffff=Failure, Data (8bit)=Success)

{

If (STRT ()) // Is the SMBus Controller Ready?

{

Return (0xFFFF)

}

Store (Zero, I2CE) // SMBus Enable

Store (0xBF, HSTS)

Store (Or (Arg0, One), TXSA) // Write Address

Store (Arg1, HCOM) // Write Command

Store (0x48, HCON) // Start + Byte Protocol

If (COMP ()) // Check if last operation completed

{

Or (HSTS, 0xFF, HSTS) // Clean up

Return (DAT0) // Success

}

Return (0xFFFF)

}

Method (SWRW, 3, Serialized)

{

If (STRT ())

{

Return (Zero)

}

Store (Zero, I2CE)

Store (0xBF, HSTS)

Store (Arg0, TXSA)

Store (Arg1, HCOM)

And (Arg2, 0xFF, DAT1)

And (ShiftRight (Arg2, 0x08), 0xFF, DAT0)

Store (0x4C, HCON)

If (COMP ())

{

Or (HSTS, 0xFF, HSTS)

Return (One)

}

Return (Zero)

}

Method (SRDW, 2, Serialized)

{

If (STRT ())

{

Return (0xFFFF)

}

Store (Zero, I2CE)

Store (0xBF, HSTS)

Store (Or (Arg0, One), TXSA)

Store (Arg1, HCOM)

Store (0x4C, HCON)

If (COMP ())

{

Or (HSTS, 0xFF, HSTS)

Return (Or (ShiftLeft (DAT0, 0x08), DAT1))

}

Return (Ones)

}

Method (SBLW, 4, Serialized) // Single Bit Line Write?

{

If (STRT ()) // Is the SMBus Controller Ready?

{

Return (Zero) // Failure

}

Store (Arg3, I2CE)

Store (0xBF, HSTS)

Store (Arg0, TXSA)

Store (Arg1, HCOM) // Write Command

Store (SizeOf (Arg2), DAT0)

Store (Zero, Local1)

Store (DerefOf (Index (Arg2, Zero)), HBDR)

Store (0x54, HCON)

While (LGreater (SizeOf (Arg2), Local1))

{

Store (0x0FA0, Local0)

While (LAnd (LNot (And (HSTS, 0x80)), Local0))

{

Decrement (Local0)

Stall (0x32)

}

If (LNot (Local0))

{

KILL ()

Return (Zero)

}

Store (0x80, HSTS)

Increment (Local1)

If (LGreater (SizeOf (Arg2), Local1))

{

Store (DerefOf (Index (Arg2, Local1)), HBDR)

}

}

If (COMP ()) // Check if last operation completed

{

Or (HSTS, 0xFF, HSTS) // Clean up

Return (One) // Success

}

Return (Zero) // Failure

}

Method (SBLR, 3, Serialized) // Single Bit Line Read?

{

Name (TBUF, Buffer (0x0100) {})

If (STRT ())

{

Return (Zero)

}

Store (Arg2, I2CE)

Store (0xBF, HSTS)

Store (Or (Arg0, One), TXSA)

Store (Arg1, HCOM)

Store (0x54, HCON)

Store (0x0FA0, Local0)

While (LAnd (LNot (And (HSTS, 0x80)), Local0))

{

Decrement (Local0)

Stall (0x32)

}

If (LNot (Local0))

{

KILL ()

Return (Zero)

}

Store (DAT0, Index (TBUF, Zero))

Store (0x80, HSTS)

Store (One, Local1)

While (LLess (Local1, DerefOf (Index (TBUF, Zero))))

{

Store (0x0FA0, Local0)

While (LAnd (LNot (And (HSTS, 0x80)), Local0))

{

Decrement (Local0)

Stall (0x32)

}

If (LNot (Local0))

{

KILL ()

Return (Zero)

}

Store (HBDR, Index (TBUF, Local1))

Store (0x80, HSTS)

Increment (Local1)

}

If (COMP ())

{

Or (HSTS, 0xFF, HSTS)

Return (TBUF)

}

Return (Zero)

}

Method (STRT, 0, Serialized) // Wait for SMBus to become ready

{

Store (0xC8, Local0) // Timeout 200ms

While (Local0)

{

If (And (HSTS, 0x40)) // IN_USE?

{

Decrement (Local0)

Sleep (One) // Wait 1ms

If (LEqual (Local0, Zero)) // timeout--

{

Return (One)

}

}

Else

{

Store (Zero, Local0) // We're ready

}

}

Store (0x0FA0, Local0) // Timeout 200ms (50us * 4000)

While (Local0)

{

If (And (HSTS, One)) // Host Busy?

{

Decrement (Local0)

Stall (0x32) // Wait 50us

If (LEqual (Local0, Zero))

{

KILL ()

}

}

Else

{

Return (Zero) // Success

}

}

Return (One) // Failure

}

Method (COMP, 0, Serialized) // Check if last operation completed

{

Store (0x0FA0, Local0) // Timeout 200ms in 50us steps

While (Local0)

{

If (And (HSTS, 0x02)) // Completion Status?

{

Return (One) // Operation Completed

}

Else

{

Decrement (Local0)

Stall (0x32)

If (LEqual (Local0, Zero))

{

KILL ()

}

}

}

Return (Zero) // Failure

}

Method (KILL, 0, Serialized) // Kill all SMBus communication

{

Or (HCON, 0x02, HCON) // Send Kill

Or (HSTS, 0xFF, HSTS) // Clean Status

}

Device (BUS0)

{

Name (_CID, "smbus")

Name (_ADR, Zero)

Device (DVL0)

{

Name (_ADR, 0x57)

Name (_CID, "diagsvault")

Method (_DSM, 4, NotSerialized)

{

Store (Package (0x03)

{

"address",

0x57,

Buffer (One)

{

Zero

}

}, Local0)

DTGP (Arg0, Arg1, Arg2, Arg3, RefOf (Local0))

Return (Local0)

}

}

}

}

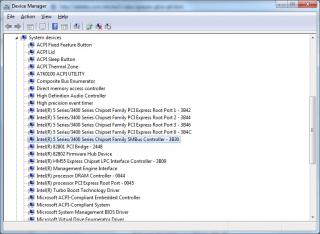

Even though I was injecting it only on Mac OS X, somehow it enable or unhidden the SMBUS controller. When boot to windows it got detected & windows installed the appropriate driver.

It is not a problem but usually it is visible in Device Manager. This show us that A42JV BIOS have buggy ACPI.

This post has been edited by kizwan: Nov 4 2010, 07:59 PM

Nov 1 2010, 12:01 AM

Nov 1 2010, 12:01 AM

Quote

Quote

0.0541sec

0.0541sec

0.42

0.42

7 queries

7 queries

GZIP Disabled

GZIP Disabled