QUOTE(ikanayam @ Nov 29 2007, 03:30 PM)

K6(-2/3) was quite a competitor on non-performance/brand-name boxes.But that's essentially... meh.

Phenom x3 and x4 now in Malaysia, The new K10

|

|

Nov 29 2007, 05:43 PM Nov 29 2007, 05:43 PM

Return to original view | Post

#1

|

Senior Member

1,955 posts Joined: Jan 2006 From: Llanfairpwllgwyngyllgogerych |

|

|

|

|

|

|

Nov 29 2007, 07:55 PM Nov 29 2007, 07:55 PM

Return to original view | Post

#2

|

Senior Member

1,955 posts Joined: Jan 2006 From: Llanfairpwllgwyngyllgogerych |

Haha, thanks. Lotsa Calculus questions and UT III playing to divert from trolling forums.

Looking at where AMD is at now (What they did with Radeon HD 3XXX) I'm pretty sure Black Edition is far, far away from their priorities. K10.5, and most ultimately, Bulldozer, is the big hitter. BDZ (lol shortform) is the only substantial thing that they can have against Intel, and it's supposed to hit the market at about H209, same time as Lynnfield (Consumer Nehalem) is introduced, maybe slightly earlier, but who knows. If 45nm SOI is a miracle (Better chance of me being bisexual But better keep your fingers open and buy Penryn first. This post has been edited by X.E.D: Nov 29 2007, 07:56 PM |

|

|

Nov 29 2007, 09:03 PM Nov 29 2007, 09:03 PM

Return to original view | Post

#3

|

Senior Member

1,955 posts Joined: Jan 2006 From: Llanfairpwllgwyngyllgogerych |

QUOTE(almostthere @ Nov 29 2007, 08:07 PM) And that's a big IF since we don't really know the real world crunching numbers and latency of Nehalem since if Intel gets it right (I'm not the betting person, but if I did, I wouldn't bet against it) we're going to see another major leap forward. As it is with Conroe/Penryn still utilising traditional NB mem controller interface to do the work and yet negate most if not all integrated mem controller's "real-world" advantages, what more if they successfully implement it and take advanatge of their large cache technology Large cache would be a means, IMC would be the end. Both would be overlapping each other in improvements, so I'm not betting too much here (except in real-world 4P+++ server tests, where Opteron Barcelona is competitive since Tigerton is still not the killer we wanted to see, where Bloomfield will kill)C2D/Qs have already pushed the FSB to hell and back, Nehalem wouldn't have that much cache, so basically it's not there where performance rules. Getting Hyperthreading "2.0" itself done would alread be quite a lot of win- Fishy says it'd be more substansial than the Northwood/Prescott flop. That, and negating off whatever performance hits C2D/C2Q had in 64-bit execution (due to Macro-ops not running?), getting the execution stages to be even wider, etc. I won't call it leapfrog in say, SuperPi or single threaded performance (I don't even reckon the difference will be more than Athlon X2 -> Core 2 Duo clock for clock percentage wise), but it would be more like a big improvement everywhere else, and much more in threaded core utilization. |

|

|

Nov 30 2007, 07:34 AM Nov 30 2007, 07:34 AM

Return to original view | Post

#4

|

Senior Member

1,955 posts Joined: Jan 2006 From: Llanfairpwllgwyngyllgogerych |

QUOTE(almostthere @ Nov 29 2007, 11:12 PM) I can't disagree with you on that but one has to consider the fact what with Intel forging ahead with larger cache at L2 instead of going L3, and at the same time developing tech which negates or reduces the latency associated with large cache, it's hard not to be imginative with what may possibly be achievable once implementation of integration is achieved and if it's inline with what the goals of HTT 2.0 are, we may see greater bandwidth being made available altho by right current microproc designs being churned out by Intel aren't that memory hungry (Correct me if I'm wrong, getting forgetful nowadays). And with that, it's possible a substantial if not leapfrogging evolution of micro-p architecture at consumer market level. As for Northwood, I can't personally agree it's a failure since it did serve it's purpose well eventhough it close to it's design limitation. Prescott and subsequently Cedar Mill should be the one's to be considered the real flops as Intel chose to prolong a design which was fast running into a performance-per-watt wall. IINM, Cedar Mill's heat density scaled to the point that at an equivalent one sqaure meter, it generated enough waste heat equivalent to a small power plant (Thanks to ikanayam for pointing out that fact last time). Was talking on Northwood at Hyperthreading level.As for Bloomfield, from what I heard from the grapevine, that seems to be a stop-gap measure although I can't get nor divulge any further details since it's unsubstantiated and/or it's based on the trust as friends Its HTT implementation was utterly useless. Nehalem could be designed with H-T in mind, and that's where I'm betting on Intel for that boost AMD can't have in synthetics (after all, synthetics are EVERYTHING in CPUs, no way bypassing them in performance assessments) Bloomfield could be a stopgap, but that would be counting on 32nm to be implemented quickly and to get Sandy Bay out fast. Which would be rather ideal as these chips are huge. |

|

|

Nov 30 2007, 06:36 PM Nov 30 2007, 06:36 PM

Return to original view | Post

#5

|

Senior Member

1,955 posts Joined: Jan 2006 From: Llanfairpwllgwyngyllgogerych |

Inquirer.

En=!In. Different publications. But both are deeply rooted from FUD. BTW errata can't always be fixed by a microcode patch. It might not be elegant too (see AMD's TLB patch with ~10% performance hit) In these cases, you better spin those babies. BTW- Core 2's Errata were lighter issues that were subsequently resolved in microcode patches without much complications. |

|

|

Dec 19 2007, 12:29 AM Dec 19 2007, 12:29 AM

Return to original view | Post

#6

|

Senior Member

1,955 posts Joined: Jan 2006 From: Llanfairpwllgwyngyllgogerych |

QUOTE(fun_feng @ Dec 11 2007, 11:48 AM) Quite suprise to see Phenom also loses on the memory benchmark. Maybe if you actually knew how the dual memory controllers work, the option to use ganged or unganged modes, and the compromise between benchmark/real-world performance, you wouldn't spout such crap.Just reinforce my opinion that the Phenom is a failure. |

|

|

|

|

|

Dec 19 2007, 05:24 PM Dec 19 2007, 05:24 PM

Return to original view | Post

#7

|

Senior Member

1,955 posts Joined: Jan 2006 From: Llanfairpwllgwyngyllgogerych |

QUOTE(t3chn0m4nc3r @ Dec 19 2007, 01:40 AM) so... u got any real world performance u wanna show wif ur X2...? i got bad enough exp wif X2 3800+ wif 4x512MB RAM on a MSI nforce 4 ultra chipset... lost to Celeron 430 on Intel 945chipset + 1GB RAM in term of software loading, networking speeds(file sharing and remote monitoring), etc... every real world performance also lost... but i partly blame it on MSI's crappy mobo... The Phenoms are not like the X2s. They have 2 memory controllers (compared to 1). They can run in ganged mode or unganged mode.My "hands on" exp as a technician proof tat Intel's core architechture outperformed AMD's X2... i also built PC's for CCTV monitoring systems... and Intel Celeron 430 on Intel 945 chipset is my best choice for best value/performance... and even reliability... One mode is faster in real-world, the other one is faster in benchmarks. I forgot which was which though. But yeah, making conclusions on single comparision numbers without descriptions = fail. My X2 works great on a 480X mobo, it's not the best OCing mobo though. For poor performance I'd blame your nForce 4 Ultra. Definitely the problem there, especially with Vista (but problems with XP too) nForce 5 is better (much better) on hard disks, and AMD's 790X is the "X38" of AMD chipsets, at P35 prices. |

|

|

Mar 16 2008, 09:37 AM Mar 16 2008, 09:37 AM

Return to original view | Post

#8

|

Senior Member

1,955 posts Joined: Jan 2006 From: Llanfairpwllgwyngyllgogerych |

Deneb should be cheap.

I mean really cheap. Really. Cheap. It's definitely <200mm^2, and while ikanayam disagrees with me on this, I suspect its diesize could be 150-70mm^2 (depends on how many HTT pads left) 150mm^2 is quite small. It's *half* a 65nm Phenom. For games and threads that run discrete (no shared data) it should be faster than current Phenoms (due to IPC increase) and for reviews showing games, that's probably all that matters. If the L3 is the obstacle to the Phenom going to higher clocks, they might get a wall broken here too. No more added latency, I might add, should also help some... |

|

|

Mar 16 2008, 10:18 AM Mar 16 2008, 10:18 AM

Return to original view | Post

#9

|

Senior Member

1,955 posts Joined: Jan 2006 From: Llanfairpwllgwyngyllgogerych |

QUOTE(ikanayam @ Mar 16 2008, 10:00 AM) http://chip-architect.com/news/Shanghai_Nehalem.jpg Well for one, looks like L3 sapped a lot of power and produced hotspots (not the wifi kind) on Barcey. I do think that it's partly responsible for the 230Mhz HTT wall considering the NB clock, IIRC scales too (the black edition chips were duds in their own right, some people reported OCs much lower than the stock 9600s even w/o the HTT wall limiting them)With 6MB L3, it's going to be around 240mm^2, about the same size as the nehalem. With a 2MB L3 (which is very likely going to be available, looking at the L3 layout), it's going to be around 180mm^2. The 2MB version might have 2 less HTT pads, but that doesn't save much. I don't think there will be 0MB L3 versions because it seems like the L3 is probably an essential part of the memory heirarchy. The L3 isn't really an issue for clocks. It runs at the memory controller clock, which is much slower than the core clock. K8x2 didn't have L3 and it was pretty good. You'd have to reconfigure the fetches, but I'm not sure L3 really did help Barcelona besides better-than-usual crosscore scaling, which HT is also part of helping. L3 shouldn't have been reintroduced. It brought AMD most of their 07 CPU problems IMHO. |

|

|

Mar 16 2008, 02:14 PM Mar 16 2008, 02:14 PM

Return to original view | Post

#10

|

Senior Member

1,955 posts Joined: Jan 2006 From: Llanfairpwllgwyngyllgogerych |

QUOTE(ikanayam @ Mar 16 2008, 10:42 AM) It is extremely unlikely for cache to cause hotspots unless there's a huge problem with the cache design. 1. TLB. 2. They're using L2 cells for L3, seems like pure cutting money on R&D and verification moolah. It might be that AMD's L2 never went above 1MB because of redundancy on K8, and they didn't discover that scaling it up would not be ideal. Oh, and getting L3/NB below 1.8Ghz is the key for current Phenom overclocking so it could be them. As for clocks, there's something in Barcelona that's being the clock/volt wall. I'm not sure it has to do with the cores themselves- not much more than K8 with some parts replaced, and still under 65 SOI... the most possible suspect might be the L3 and MC. |

|

|

Apr 4 2008, 06:35 AM Apr 4 2008, 06:35 AM

Return to original view | Post

#11

|

Senior Member

1,955 posts Joined: Jan 2006 From: Llanfairpwllgwyngyllgogerych |

Now you're just wayy off.

6000+ can't even compete in cases like this. In TF2 with 500Mhz less the Phenom still scores close. 9850 Black Edition is now OCed to 3.5Ghz (with custom SPD too), and can hit 3Ghz on air if you have a later (NOT a review batch)/ lucky chip. Otherwise, 3.2 on water should be doable. Even later 9600 BEs would start to do 3Ghz on water already. http://www.xtremesystems.org/forums/showthread.php?t=183025 This post has been edited by X.E.D: Apr 4 2008, 06:39 AM |

|

|

Apr 4 2008, 10:07 PM Apr 4 2008, 10:07 PM

Return to original view | Post

#12

|

Senior Member

1,955 posts Joined: Jan 2006 From: Llanfairpwllgwyngyllgogerych |

Some guy from OCZ did custom SPDs and more tweaking (what OC should be, not up FSB/Multi and call that a *conclusion*)

Techreport only went on the Multiplier. A definite no-no in reaching a "max clock". Somebody said gaming- even in other cases a 6000+ would be lacking either way. How much more can you push that instead? Not much I reckon. This post has been edited by X.E.D: Apr 4 2008, 10:11 PM |

|

|

Apr 5 2008, 12:43 AM Apr 5 2008, 12:43 AM

Return to original view | Post

#13

|

Senior Member

1,955 posts Joined: Jan 2006 From: Llanfairpwllgwyngyllgogerych |

QUOTE(ikanayam @ Apr 4 2008, 11:20 PM) You want to isolate just the CPU when finding the max cpu clock. So adjusting multipliers is the best way to do this, to keep memory from affecting the overclock. If you want to go to extremes, a much less extreme intel overclock will easily smack the phenom anyway so it's pointless either way. Yes they would, but knowing that Agena's design isn't killing its clocks w/o respect to TDP is a relief. Even K8BE tops out at 3.6 for most.Oh, and the Asus board seems to be killing performance quite some. X3 (Lex's EXP link) 2.3 gets 1.8k / Single Core in Cinebench, X4 @ 3.2 gets 3.4k / 1Core. |

|

|

|

|

|

Apr 9 2008, 08:46 PM Apr 9 2008, 08:46 PM

Return to original view | Post

#14

|

Senior Member

1,955 posts Joined: Jan 2006 From: Llanfairpwllgwyngyllgogerych |

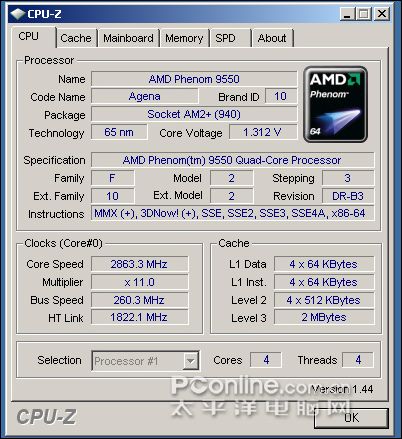

Phenom 9550s (The RM500-600 one) OCs to 2.8Ghz at 1.312v (I think it's stock volt for the 9750/9850, 9550 not sure)

I suspect it's the HTT limiting you, but it's no longer stuck at 230Mhz. This time it's 260Mhz. So a 9750 theoratically can reach 3.1Ghz and still be cheaper than the BE. http://diy.pconline.com.cn/cpu/reviews/0804/1262586_7.html  This post has been edited by X.E.D: Apr 9 2008, 08:54 PM |

|

|

Apr 10 2008, 06:16 PM Apr 10 2008, 06:16 PM

Return to original view | Post

#15

|

Senior Member

1,955 posts Joined: Jan 2006 From: Llanfairpwllgwyngyllgogerych |

@Bata

CERTAIN 780G motherboards will NOT! support Phenom 9850 BE and Athlon X2 6000+. Most of them out now will NOT support it. Those mobos have 4 stage PWMs that will blow when any 125W CPU is inserted. 770X and some 790X (MSI K9A2 CF) will NOT support these too in current revisions. I think the J&W 780G board has more PWMs, and a DFI board is coming (obviously, 6-12 stage |

|

|

Apr 10 2008, 07:16 PM Apr 10 2008, 07:16 PM

Return to original view | Post

#16

|

Senior Member

1,955 posts Joined: Jan 2006 From: Llanfairpwllgwyngyllgogerych |

http://www.gigabyte.com.tw/Support/Motherb...?ProductID=2758

Gigabyte 780G is okay, but if your customer wants to OC, just get him an MSI K9A2 Platinum. It's about RM500 but has tons of features and is definitely worth it. As for integrated graphics, I don't think someone wants to use a 9850BE with THAT. |

|

|

Apr 10 2008, 07:40 PM Apr 10 2008, 07:40 PM

Return to original view | Post

#17

|

Senior Member

1,955 posts Joined: Jan 2006 From: Llanfairpwllgwyngyllgogerych |

Sorry bata, the ECS does not support 125W CPUs.

The Abit AX78 does (6400+ and FX-62 are 125W), but the BIOS for 9850 hasn't come yet. This is much cheaper than 790FX though you'll have to choose a graphics card. This post has been edited by X.E.D: Apr 10 2008, 07:42 PM |

|

|

Apr 10 2008, 08:56 PM Apr 10 2008, 08:56 PM

Return to original view | Post

#18

|

Senior Member

1,955 posts Joined: Jan 2006 From: Llanfairpwllgwyngyllgogerych |

I checked the Biostar 780G, same conclusion as the AX78- good design, no BIOS yet.

If the Athlon X2 6000+, 6400+ and FX-62 is/are supported, chances are that Phenom's not gonna fry your mobo. However, wait for the BIOSes to come first before actually purchasing, as Taiwan OEMs have terrible support. |

|

|

Apr 15 2008, 10:34 AM Apr 15 2008, 10:34 AM

Return to original view | Post

#19

|

Senior Member

1,955 posts Joined: Jan 2006 From: Llanfairpwllgwyngyllgogerych |

Mobo should blow if the MOSFETs are not able to handle the load/overheat.

At min, the system will become permanently unstable. 790FX boards are all okay. |

|

|

Apr 15 2008, 10:00 PM Apr 15 2008, 10:00 PM

Return to original view | Post

#20

|

Senior Member

1,955 posts Joined: Jan 2006 From: Llanfairpwllgwyngyllgogerych |

It's not the chipset itself, it's the specific motherboard design la.

|

|

Topic ClosedOptions

|

| Change to: |  0.0289sec 0.0289sec

0.44 0.44

7 queries 7 queries

GZIP Disabled GZIP Disabled

Time is now: 8th December 2025 - 12:05 PM |