[Cpu-Z question]

[Cpu-Z question]

|

|

Dec 13 2007, 04:52 PM, updated 18y ago Dec 13 2007, 04:52 PM, updated 18y ago

Show posts by this member only | Post

#1

|

Junior Member

67 posts Joined: Dec 2007 |

|

|

|

|

|

|

Dec 13 2007, 04:57 PM Dec 13 2007, 04:57 PM

Show posts by this member only | Post

#2

|

|

Elite

5,784 posts Joined: Jan 2003 From: Shah Alam |

dual channel....

|

|

|

Dec 13 2007, 04:59 PM Dec 13 2007, 04:59 PM

Show posts by this member only | Post

#3

|

Senior Member

1,237 posts Joined: Jul 2006 From: espie-prai |

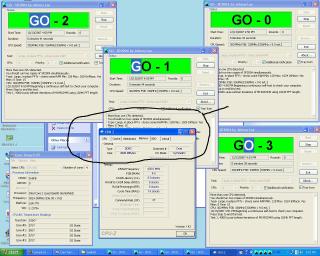

i dunno about that..but i think u should running dual orthos only..not until 4...based on ur proc were quad core..

1 orthos = dual core 2 orthos = quad core |

|

|

Dec 13 2007, 05:00 PM Dec 13 2007, 05:00 PM

Show posts by this member only | Post

#4

|

Junior Member

67 posts Joined: Dec 2007 |

|

|

|

Dec 13 2007, 05:59 PM Dec 13 2007, 05:59 PM

Show posts by this member only | Post

#5

|

Senior Member

971 posts Joined: Aug 2006 From: Penang |

If I'm not mistaken, symmetric here means that the both channels of the dual channel memory controller operate together, transferring 128bits at one shot each time. Asymmetric should be 2 single channels operating together, each transfering 64bits for a total of 128bits. By this convention, an asymmetric setup allows for 2 seperate memory requests to be made at the same time while for symmetric memory requests must be queued, but can handle large blocks at one time.

I'm guessing this based on the explaination given for the new AMD quad cores, which call this modes "ganged" and "unganged". Having memory controllers operate seperately means more cores can have their memory requests fulfilled while having all four share a single, high bandwidth controller means they have to queue up and wait. |

|

Topic ClosedOptions

|

| Change to: |  0.0176sec 0.0176sec

0.40 0.40

6 queries 6 queries

GZIP Disabled GZIP Disabled

Time is now: 1st December 2025 - 11:58 AM |