QUOTE(ben_panced @ Oct 18 2011, 09:21 AM)

the problem with bd is

although the front end got like 4 instruction decoder, but it is shared by two cores, and the decoder can only service 1 core at a time, contributing to its slowness in ST..

furthermore, each core only has 2 integer ALU compared to 4 in intel cpus starting fro C2D.. so you get the point why this BD performance is very underwhelming..

couple it with a long instruction pipeline and a very high latency cache..

and you got your self a very slow CPU

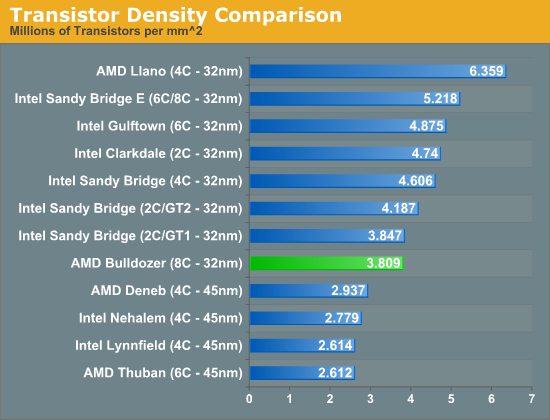

AMD claims that the third integer ALU in Phenom II is not used therefore it is removed in BD. How would that affect the performance significantly is not known but from the benchmarks it is clear that something is lacking with BD when it loses to its predecessors and Intel. The long instruction pipeline is meant so that BD could achieve a higher clock speed but at the cost of its IPC, as to why AMD wants this I wouldn't know as Netburst has already proved that this method is not effective. AMD's L3 cache is a huge chunk of 8MB cache shared by all of the 8 cores, so latency is to be expected. Intel's approach is four 2MB LLC not shared and with a ring bus to connect all of them so latency might not be bigger with smaller caches per core.although the front end got like 4 instruction decoder, but it is shared by two cores, and the decoder can only service 1 core at a time, contributing to its slowness in ST..

furthermore, each core only has 2 integer ALU compared to 4 in intel cpus starting fro C2D.. so you get the point why this BD performance is very underwhelming..

couple it with a long instruction pipeline and a very high latency cache..

and you got your self a very slow CPU

QUOTE(bai1101 @ Oct 18 2011, 09:32 AM)

Confuse with all the technical talk.

For the first time I see a product that create so many discuss.

That's what we're here for. For the first time I see a product that create so many discuss.

Oct 18 2011, 11:57 AM

Oct 18 2011, 11:57 AM

Quote

Quote

0.0206sec

0.0206sec

0.67

0.67

7 queries

7 queries

GZIP Disabled

GZIP Disabled